자일링스는 4단계 PAM4(Pulse Amplitude Modulation) 전송 체계를 이용해 56G 트랜시버 기술을 실행하는 16nm FinFET+ 기반의 프로그래머블 디바이스를 개발했다고 밝혔다.

업계에서 차세대 라인 레이트로 확장성이 가장 뛰어난 시그널링 프로토콜로 인정받고 있는 PAM4 솔루션은 기존 인프라 대역폭을 2배로 늘려 광학 및 구리 인터커넥트를 위한 새로운 이더넷 배치를 도와준다. 자일링스는 PAM4가 대중화되기에 앞서 현재 56G의 혁신 기술을 도입해 선보이며, 공급자 및 에코시스템 회원사들의 교육을 돕고 변화에 대비하고 있다.

자일링스의 SerDes 기술 그룹의 부사장, 켄 창(Ken Chang)은 “자일링스 고객들은 차세대 애플리케이션을 어떻게 가속시킬지 이미 예상하고 있다. 자일링스는 현재 56G PAM4 기술 솔루션에 대한 인식을 제고하여 고객이 디자인 변화에 대비할 수 있도록 돕고자 한다”고 말하며, “자사의 기술을 선보일 수 있게 되어 기쁘다”고 전했다.

클라우드 컴퓨팅, 산업용 사물인터넷(IIoT), 소프트웨어 정의 네트워크(SDN, Softward-Defined Network)와 같이 트렌드가 무한한 대역폭의 필요성을 높이고 촉진함에 따라 기술 혁신은 50G, 100G, 400G 포트 확장은 물론이며, 비용과 비트당 전력을 늘리지 않고도 테라비트 인터페이스로 포트 밀도를 극대화해야 한다.

표준화된 차세대 라인 레이트는 이러한 지속적인 대역폭 요건을 충족하는데 무엇보다 중요하다. 자일링스는 옵티컬 인터네트워킹 포럼(OIE, Optical Internetworking Forum)과 IEEE(Institute of Electrical and Electronics Engineers) 모두에서 56G PAM4를 표준화하고자 선도하고 있다.

자일링스의 56G PAM4 트랜시버 기술은 삽입 손실(insertion loss)과 크로스토크(crosstalk)를 포함한 라인 레이트에서 기존 데이터 전송의 물리적 한계를 극복하기 위해 개발되었다. 이것은 칩투칩, 모듈, 직접 부착 케이블, 백플레인 애플리케이션에서 구리 및 광학 인터커넥트를 지원한다. 또한 이는 테라비트 라인 카드를 뛰어넘어 400G에서 테라비트 섀시 백플레인까지 차세대 시스템 디자인을 가능하게 한다.

TSMC 북미 부사장인 지브 달랄(Sajiv Dalal)은 “TSMC는 자일링스와 협력하여 16nm FinFET+를 위한 PAM4 디바이스를 준비하고 있다”고 전하며, “이 혁신적인 트랜시버는 자일링스와 오랫동안 이어온 협력의 결과물이다. TSMC는 고성능 컴퓨팅에 전념하고 있으며, 이 달 말에 있을 자일링스의 선도적인 기술 시연을 기대하고 있다”고 덧붙였다.

뉴스타운

뉴스타운TV 구독 및 시청료 후원하기

뉴스타운TV

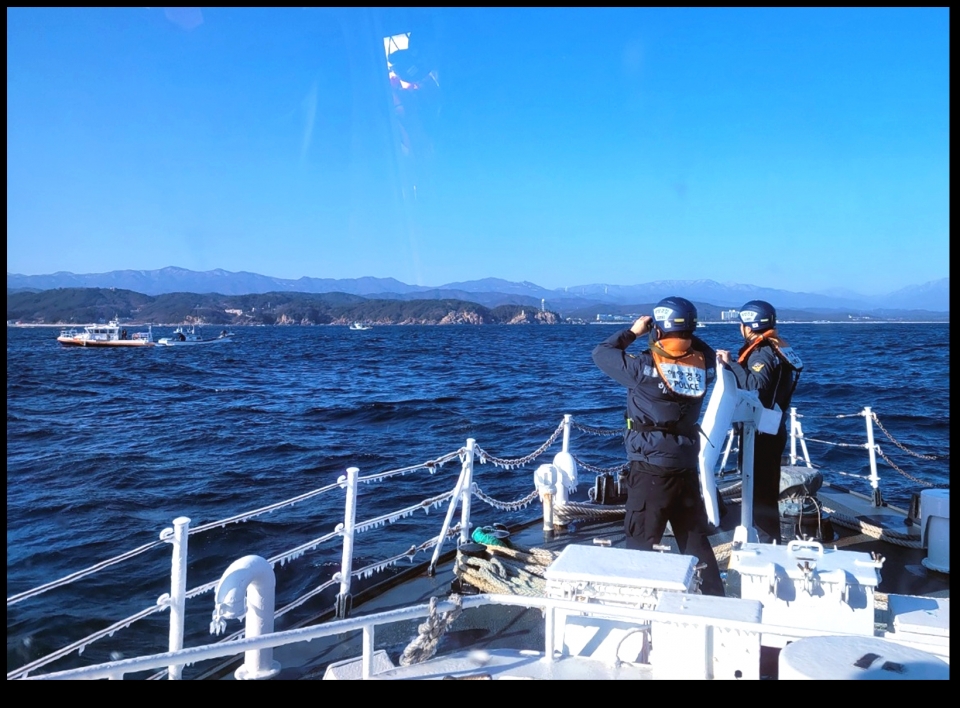

![[단독] 북한산 인수봉, 구조 헬기 긴급 출동 장면 포착!](/news/photo/202511/669971_628773_447.jpg)